机载网络化测试系统专用IEEE1588千兆交换机设计

打开文本图片集

中图分类号:TB9 文献标志码:A文章编号:1674-5124(2025)07-0120-09

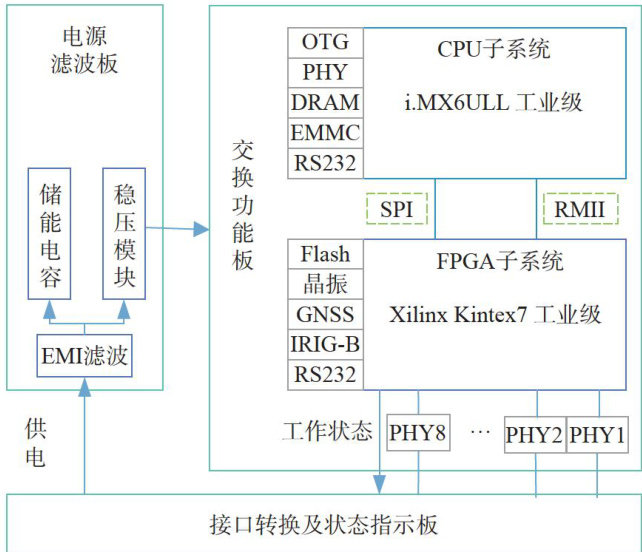

Abstract: To address the technical challenges in airborne networked test systems—such as interoperability barriers between IEEE1588-2002 (v1) and IEEE1588-2008 (v2) devices, implementation diffculties of v1 protocol in gigabit environments, poor vl synchronization accuracy in cascaded networks,and inefficient data filtering-a specialized gigabit switch design based onan FPGA + CPU heterogeneous architecture is proposed. Key innovations include: 1) A protocol conversion middleware to bridge v1-v2 heterogeneous networking; 2) A colaborative framework integrating low-jiter gigabit physical-layer (PHY) chips and FPGA logic to achieve precise vl timing synchronization; 3)A cascaded synchronization method leveraging transparent clock correction mechanism to mitigate multi-level synchronization errors; 4)A high-speed data filtering engine based on atermary content addressable memory (TCAM) architecture, enabling parallel matching of 512 filtering rules.Laboratory tests demonstrate that under harsh conditions (-40-70∘C) ,the switch achieves cascaded v1/v2 synchronization errors below 2O0 ns and stable data filtering latency within 8O ns.Flight tests validateitscapabilityto fulfill critical airborne requirements,including sub-microsecond clock synchronization,compatibility with hybrid protocol devices,and high-performance data filtering,thereby 收稿日期:2025-02-19;收到修改稿日期:2025-03-21 作者简介:李峰(1981-),男,陕西咸阳市人,高级工程师,硕士,研究方向为飞机机载测试技术。(剩余11277字)