通用并行CRC计算方法及FPGA实现

打开文本图片集

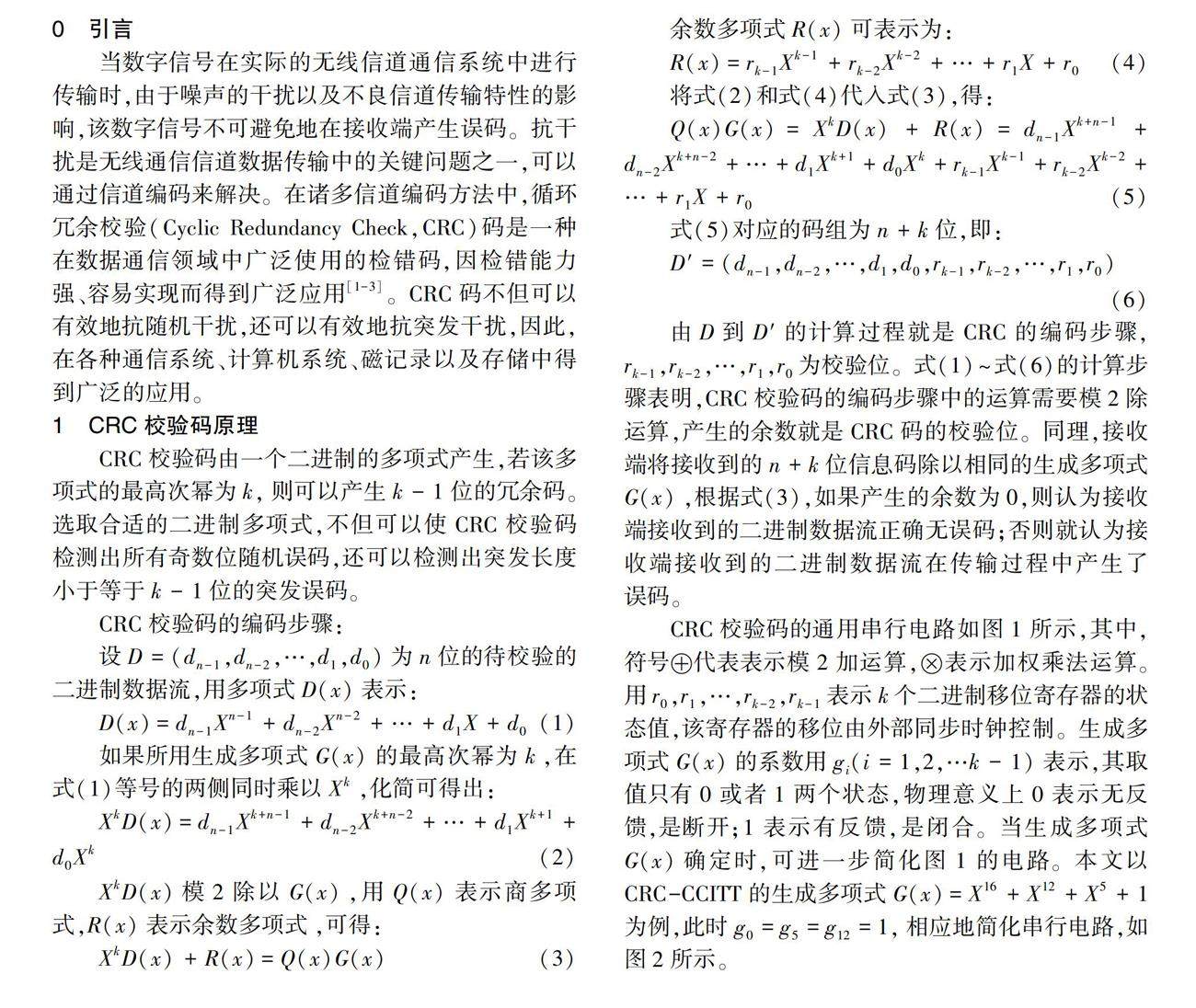

摘要:循环冗余校验(CRC)码是诸多信道编码方式中最常用的一种编码,也是一种检错概率高且容易硬件实现的检错码,因检错能力强、容易实现而得到广泛应用。首先,本文介绍了循环冗余校验的算法原理,分析了CRC校验码的具体运算过程;其次,本文在原算法的基础上提出一种高速并行CRC算法,并以CRC-CCITT为例,推导出8位并行运算的CRC- CCITT逻辑关系式;最后,本文根据推导的8位并行运算的逻辑关系式,描述了8位并行的CRC- CCITT硬件实现电路。(剩余4786字)