基于FPGA的AES密钥扩展算法优化设计

打开文本图片集

中图分类号:TN918.4 文献标志码:A 文章编号:1673-5072(2025)04-0428-06

Optimized Design of AES Key Expansion Algorithm Based on FPGA

WENQiang-qiang,XIAO Shun-wen,FENG Cui-lian,HUANG Hong-yi (School ofElectronic InformationEngineering,ChinaWestNormal University,Nanchong Sichuan637o09,China)

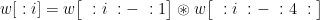

Abstract:Aiming atthe defectthatthe correlation between adjacent rounds of keys obtained by the key expansion algorithm in the traditional AES algorithm was too strong,a key expansion algorithm based on FPGA optimisation was proposed.The derivation principles of the traditional AES key expansion algorithm as well as the inverse algorithm were studied and analysed,and the optimized key expansion algorithm was proposed according to the reversibility of the Exclusive OR(XOR)operation in logic algebra and the characteristics of the T operation.The experimental results show that the optimized key expansion algorithm attenuates the correlation of adjacent rounds of keys,and can be correctly applied to the AES encryption and decryption algorithm.The algorithm notonly enhances the security,but also retains the high efficiencyand fastnessofthe original algorithm,and there is acertain improvement in key indexes such as the resource consumption and maximum frequency of FPGA.

Keywords:AES;key expansion algorithm;FPGA optimisation;logical algebra ;security

高级加密标准 AES 算法是目前最广泛使用的对称加密算法之一[1],因其安全性高、计算效率优越,被应用于车联网通信加密、数据加密、安全协议等众多领域[2]。(剩余7356字)